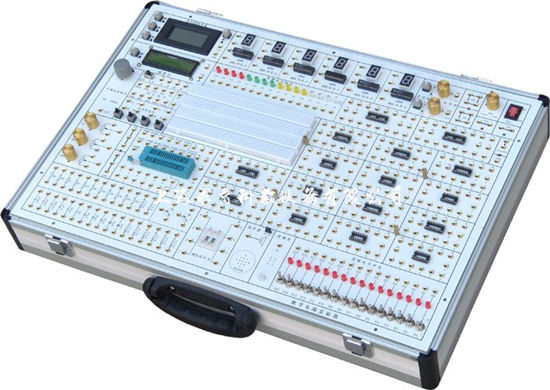

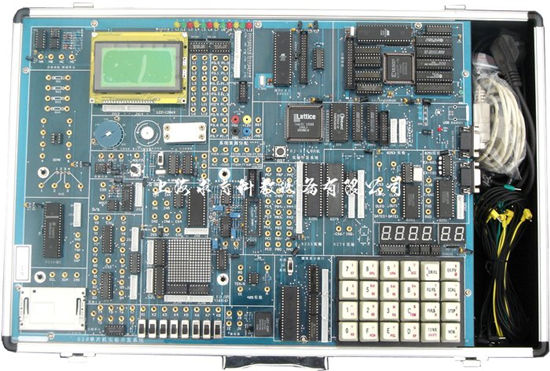

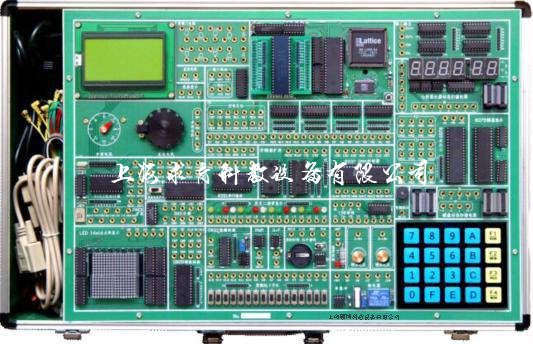

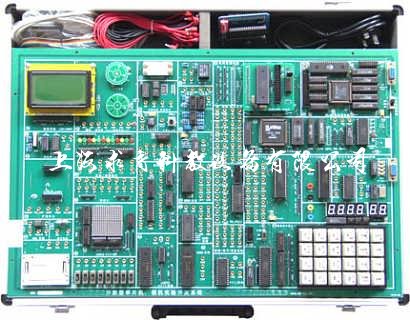

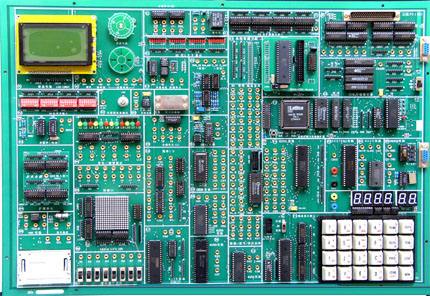

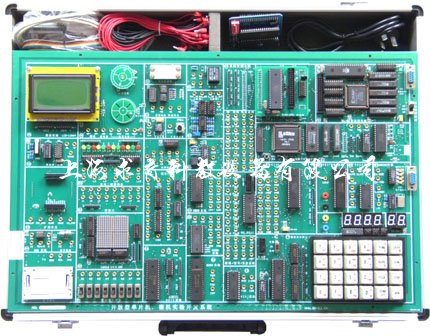

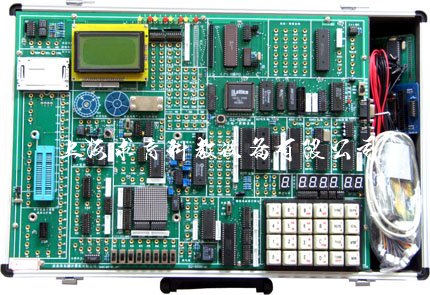

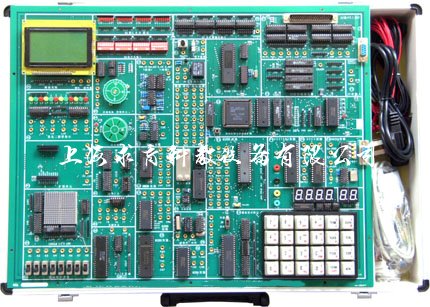

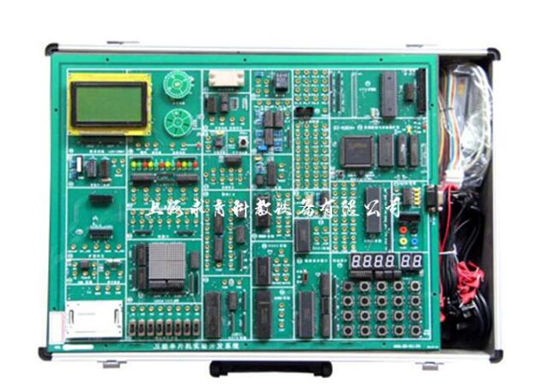

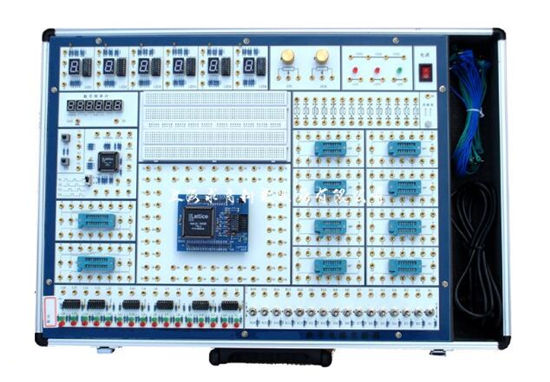

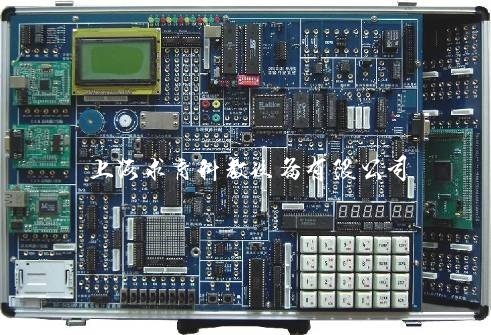

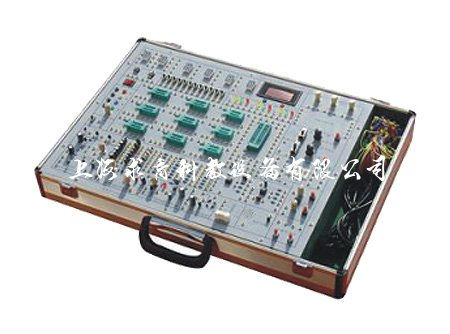

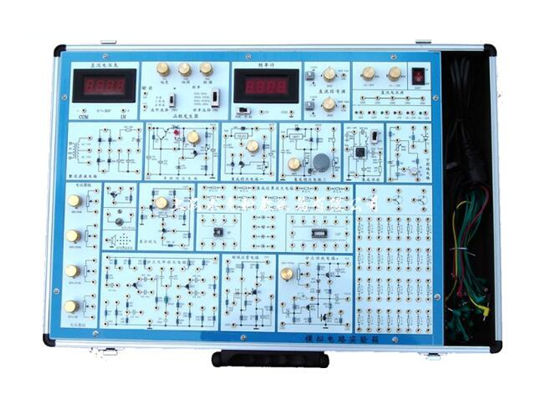

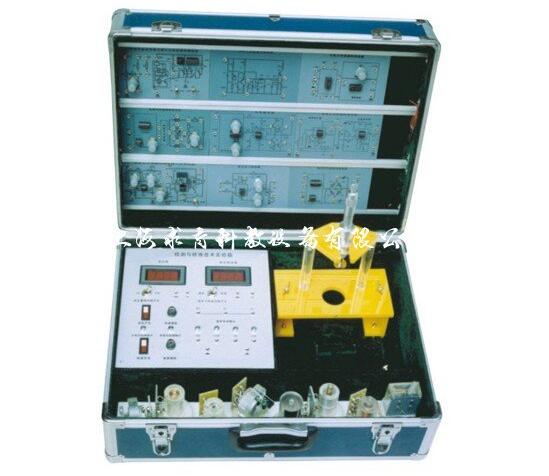

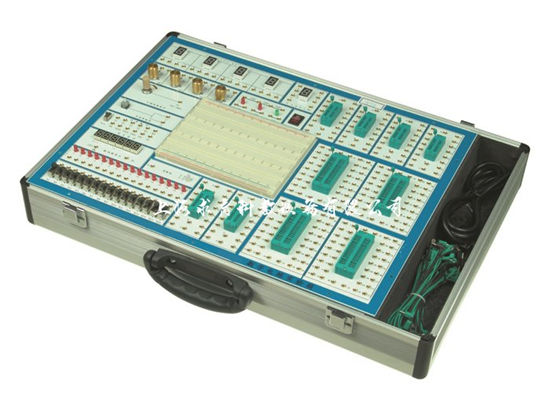

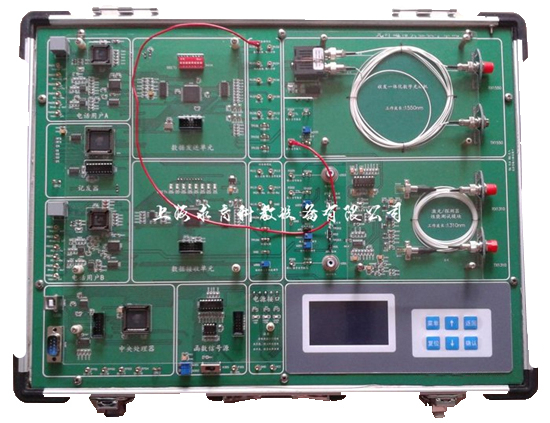

上海求育QY-JXSY10型EDA实验开发系统实验箱采用主板(基本实验系统)加适配板(下载板)的双板式结构,适配板可选配Altera,Lattice,Xilinx等ISP或现场配置的CPLD/FPGA进行编程下载.实验箱提供良好的混合电压(MV)兼容功能,具备了5V、3.3V、2.5V、1.8V不同芯核电压的CPLD/FPGA器件编程下载和实验开发的全兼容功能。因此,用户可避免单5V的EDA实验系统过时淘汰之虑。电话021-69918115

详细信息:https://www.mmaan.com/cpjs/1583.html

上海求育QY-JXSY10型EDA实验开发系统实验箱实验项目:

基本实验:

(1)七人表决器;

(2)四位加法器;

(3)BCD码加法器;

(4)格雷码变换器;

(5)四位并行乘法器;

(6)触发器;

(7)用ABEL语言设计74LS160功能模块计数器;

(8)多模加减计数器

(9)可控脉冲发生器;

(10)简易数码锁;

(11)英语字母显示实验;

(12)八位乘法器;

(13)序列检测器;

(14)可变模16位加法计数器;

(15)正负脉冲数控调制发生器;

(16)秒表。

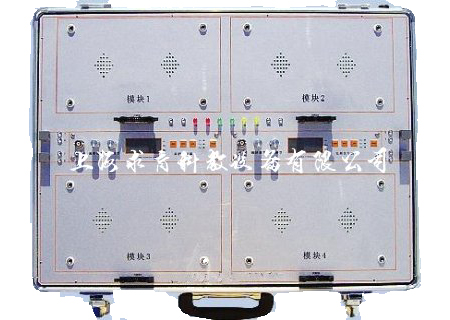

模块实验:

(1)A/D 0809模数转换器实验;

(2)D/A 0832数模转换器实验;

(3)步进电机控制实验;

(4)16*16 LED点阵显示实验;

(5)电子时钟实验;

(6)数码管静态显示实验;

(7)VGA接口彩条信号实验;

(8)4*4键盘扩展实验;

(9)128*64 LCD液晶显示实验;

(10)电子音乐演奏实验;

(11)RS232串口发送实验(SEND);

(12)RS232串口接收实验(RECEIVE);

(13)PS/2键盘接口逻辑设计;

(14)单片机总线接口实验;

(15)异步串口通讯(UART)

数字系统设计:

(1)数字钟;

(2)频率计;

(3).交通灯;

(4)数字锁;

(5)出租车计费器;

(6)抢答器;

(7)自动电梯;

(8)彩灯控制器等。

CPLD/FPGA简介

CPLD主要是由可编程逻辑宏单元(LMC,Logic Macro Cell)围绕中心的可编程互连矩阵单元组成,其中LMC逻辑结构较复杂,并具有复杂的I/O单元互连结构,可由用户根据需要生成特定的电路结构,完成一定的功能。由于 CPLD内部采用固定长度的金属线进行各逻辑块的互连,所以设计的逻辑电路具有时间可预测性,避免了分段式互连结构时序不完全预测的缺点。较常用的有Altera公司的CPLD。

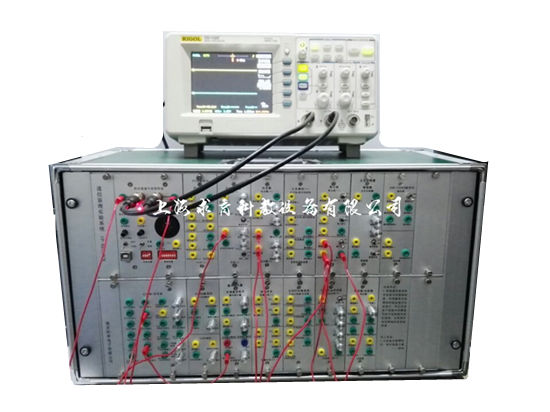

FPGA通常包含三类可编程资源:可编程逻辑功能块、可编程I/O块和可编程互连。可编程逻辑功能块是实现用户功能的基本单元,它们通常排列成一个阵列,散布于整个芯片;可编程I/O块完成芯片上逻辑与外部封装脚的接口,常围绕着阵列排列于芯片四周;可编程内部互连包括各种长度的连线线段和一些可编程连接开关,它们将各个可编程逻辑块或I/O块连接起来,FPGA在可编程逻辑块的规模,内部互连线的结构和采用的可编程元件上存在较大的差异。FPGA一 般用于逻辑仿真。电路设计工程师设计一个电路首先要确定线路,然后进行软件模拟及优化,以确认所设计电路的功能及性能。

随着电路规模的不断增大,电路频率的不断提高,将给电路引入许多分布参数的影响,而这些影响用软件方法较难进行仿真,所以有必要进行硬件仿真。FPGA就可以进行硬件仿真以做成模型机。将软件模拟后的路径下载到FPGA,就可容易的到一个模型机。从改模型机,设计者就可以很直观的测试其逻辑功能以及性能指标。