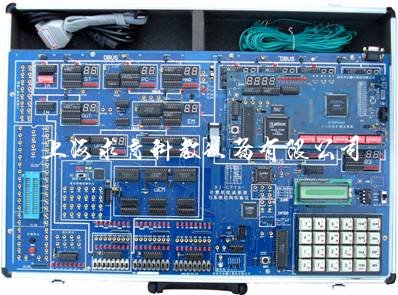

上海求育QY-JXSY30计算机组成原理与系统结构实验箱是一款八位,十六位兼容设计的计算机组成原理和系统结构实验仪,系统由八位机主板和十六位机扩展实验板组成.主板以八位机模式,用TTL74系列器件加多片在线可编程CPLD构建模型机部件,扩展实验板以十六位机模式,用12万门EP1C6芯片构建模型机所有部件,在对八位机了解的基础上,让学生对十六位计算机组成原理有更深刻的理解,系统软件提供了详尽的信息窗口、运行图表和多类帮信息,使教学的过程轻松自如。电话021-69918115

详细信息:https://www.mmaan.com/cpjs/1561.html

实验项目

(1)寄存器读写实验

(2)运算器八种运算实验

(3)数据输出/移位实验

(4)UPC实验

实验1:UPC加1实验

实验2:UPC打入实验

(5)PC实验

实验1:PC加1实验

实验2:PC打入实验

(6)存贮器读写实验

(7)微程序读写实验

(8)中断实验

(9)模型机综合实验(微程控制器)

实验1:数据传送/输入/输出实验

实验2:数据运算实验(加/减法/或)

实验3:移位/取反实验

实验 4:转移实验

实验 5:调用实验

实验 6:中断实验

实验 7:指令流水实验

实验 8:RISC模型机

(10) 组合逻辑控制器实验

(11) 设计指令/微指令系统.

(12) 扩展实验

实验1:8255扩展I/O口实验

实验 2:8253扩展定时器实验

注:实验(1)-(8)为手动微代码控制,(9)-(12)为微程序或组合逻辑控制.

十六位机扩展部分实验☆(可选配)

(13)十六位ALU 实验

(14)十六位寄存器实验

(15)十六位寄存器组实验

(16)十六位指令计数器PC 实验

(17)中断控制实验

(18)十六位模型机的总体实验

说明:实验项目打“☆”号为选配实验。

实验一:通用寄存器实验

一、实验目的

1. 熟悉通用寄存器的数据通路。

2. 掌握通用寄存器的构成和运用。

二、实验要求

在掌握了AX、BX运算寄存器的读写操作后,继续完成CX、DX通用寄存器的数据写入与读出。

三、实验原理

实验中所用的通用寄存器数据通路如下图所示。由四片8位字长的74LS574组成CX(R1 R0)、DX(R3 R2)通用寄存器组。图中X2 X1 X0定义输出选通使能,SI、XP控制位为源选通选择。RXW为寄存器数据写入使能,OP、DI为目的寄存器选择。DRCK信号为寄存器写脉冲,下降沿有效。准双向I/O输入输出端口用于置数操作,经2片74LS245三态门与数据总线相连。

图2-3-3通用寄存器数据通路

四、实验内容

1. 实验连线

| 连线 | 信号孔 | 接入孔 | 作用 | 有效电平 |

| 1 | DRCK | CLOCK | 单元手动实验状态的时钟来源 | 下降沿打入 |

| 2 | W | K6(M6) | 总线字长:1=16位字操作,0=8位字节操作 | |

| 3 | X2 | K10(M10) | 源部件定义译码端X2 |

三八译码 八中选一 |

| 4 | X1 | K9(M9) | 源部件定义译码端X1 | |

| 5 | X0 | K8(M8) | 源部件定义译码端X0 | |

| 6 | SI | K19(M19) | 源寄存器编址:1=CX,0=DX,定义到M19 | |

| 7 | XP | K7(M7) | 源寄存器奇偶位:1=偶寻址,0=奇寻址 | |

| 8 | RXW | K18(M18) | 寄存器写使能,本例定义到M18位 | 高电平有效 |

| 9 | DI | K17(K17) | 目标寄存器编址:1=CX,0=DX,定义到M17 | |

| 10 | OP | K16(M16) | 目标寄存器奇偶位:1=偶寻址,0=奇寻址 |

2. 寄存器的读写操作

① 目的通路

当RXW=1时,由DI、OP编码产生目的寄存器地址,详见下表。

| 表2.3.5 通用寄存器“手动/搭接”目的编码 | |||||

| 目标使能 | 通用寄存器目的编址 | 功能说明 | |||

| RXW | DI | OP | W | DRCK | |

| 1 | 1 | 1 | 1 | ↓ | CX字写 |

| 1 | 1 | 1 | 0 | ↓ | CL(R0)偶字节写 |

| 1 | 1 | 0 | X | ↓ | CH(R1)奇字节写 |

| 1 | 0 | 1 | 1 | ↓ | DX字写 |

| 1 | 0 | 1 | 0 | ↓ | DL(R2)偶字节写 |

| 1 | 0 | 0 | X | ↓ | DH(R2)奇字节写 |

② CX、DX寄存器的写入

通过“I/O输入输出单元”向CX、DX分别置数1122h、3344h,操作步骤如下:

③ 源通路

当X2 X1 X0=1 1 0时,由SI、XP编码产生源寄存器,详见下表。

| 表2.3.6 通用寄存器“手动/搭接”源编码 | ||||||

| 源使能 | 通用寄存器源编址 | 功能说明 | ||||

| X2 | X1 | X0 | SI | XP | W | |

| 1 | 1 | 0 | 1 | 1 | 1 | CX字读 |

| 1 | 1 | 0 | CL(R0)偶字节读 | |||

| 1 | 0 | X | CH(R1)奇字节读 | |||

| 0 | 1 | 1 | DX字读 | |||

| 0 | 1 | 0 | DL(R2)偶字节读 | |||

| 0 | 0 | X | DH(R2)奇字节读 | |||

④ CX、DX寄存器的读出

关闭CX、DX写使能,令RXW(K18)=0,按下流程分别读CX、DX。

实验二:准双向I/O口实验

一、实验目的

熟悉与了解准双向I/O口的构成原理。

二、实验要求

掌握准双向I/O口的输入/输出特性的运用。

三、实验原理

Dais-CMX16+向用户提供的是按准双向原理设计的十六位输入/输出I/O口,当该位为“1”时才能用作输入源,上电或复位(手动态按【返回】键),该十六位I/O口被置位(即为“FFFFh”)。通常情况下,在用作输入的时候就不能再有输出定义。电路结构如图2-3-4所示。该口外接十六位二进制数据开关,适用于外部数据的输入,该口跨接十六个发光二极管,经缓冲驱动四个七段显示,能以二进制和十六进制两种方式显示I/O口的输入输出状态。发光管在高电平“1”时发光点亮。

图2-3-4 准双向I/O电路

实验中所用的I/O口数据通路如图2-3-5所示。I/O的输入经2片74LS245缓冲与数据总线相连,I/O口的输出由2片74LS574锁存后输出,锁存器的输入端与数据总线相连。

图2-3-5 I/O口数据通路

四、实验内容

1. 实验连线

| 连线 | 信号孔 | 接入孔 | 作用 | 有效电平 |

| 1 | IOCK | CLOCK | 单元手动实验状态的时钟来源 | 下降沿打入 |

| 2 | W | K6(M6) | 总线字长:1=16位字操作,0=8位字节操作 | |

| 3 | X2 | K10(M10) | 源部件定义译码端X2 |

三八译码 八中选一 |

| 4 | X1 | K9(M9) | 源部件定义译码端X1 | |

| 5 | X0 | K8(M8) | 源部件定义译码端X0 | |

| 6 | XP | K7(M7) | 源奇偶位:1=偶寻址,0=奇寻址 | |

| 7 | IOW | K17(M17) | I/O写使能,本例定义到M17位 | 高电平有效 |

| 8 | OP | K16(M16) | 目的奇偶位:1=偶寻址,0=奇寻址 | |

| 9 | RXW | K19(M19) | 寄存器写使能,本例定义到M19位 | 高电平有效 |

| 10 | DI | K18(K18) | 目标寄存器编址:1=CX,0=DX,定义到M18 |

2. 搭接方式I/O的寻址定义

| I/O口源编址 | I/O口目的编址 | ||||||||||

| 源编码 | I/O编址 | 注释 | 目的I/O编址 | 注释 | |||||||

| X2 | X1 | X0 | W | XP | IOW | W | OP | IOCK | |||

| 0 | 1 | 1 | 1 | 1 | IO字读 | 1 | 1 | 1 | ↓ | IO字写 | |

| 0 | 1 | IOL偶字节读 | 0 | 1 | ↓ | IOL偶字节写 | |||||

| X | 0 | IOH奇字节读 | X | 0 | ↓ | IOH奇字节写 | |||||

3. I/O口写操作(输出)

执行OUT I/O,AX 指令,把AX内容送I/O口。

4. I/O口读操作(输入)

执行IN CX,I/O指令,把I/O口内容送CX。

5. I/O口的字节操作(偶输入,奇输出)

执行OUT IOH,IOL 指令,把S7~S0送S15~S8。

实验三:十六位机运算器实验

一、实验目的

完成算术、逻辑、移位运算实验,熟悉ALU运算控制位的运用。

二、实验原理

实验中所用的运算器数据通路如图2-4-1所示。ALU运算器由CPLD描述。运算器的输出经过2片74LS245三态门与数据总线相连,2个运算寄存器AX、BX的数据输入端分别由4个74LS574锁存器锁存,锁存器的输入端与数据总线相连,准双向I/O输入输出端口用来给出参与运算的数据,经2片74LS245三态门与数据总线相连。

图2-4-1 运算器数据通路

图中AX、BX的写控制由O2~O0编码定义,通过按【单拍】钮完成运算源的数据打入。

三、运算器功能编码

表2.4.1 ALU运算器编码表

| 算术运算 | 逻辑运算 | |||||||||

| K15 | K13 | K12 | K11 | 功能 | K15 | K13 | K12 | K11 | 功能 | |

| M | S2 | S1 | S0 | M | S2 | S1 | S0 | |||

| 1 | 1 | 1 | 1 | A+B+C | 0 | 1 | 1 | 1 | B | |

| 1 | 1 | 1 | 0 | A—B—C | 0 | 1 | 1 | 0 | /A | |

| 1 | 1 | 0 | 1 | RLC | 0 | 1 | 0 | 1 | A-1 | |

| 1 | 1 | 0 | 0 | RRC | 0 | 1 | 0 | 0 | A=0 | |

| 1 | 0 | 1 | 1 | A+B | 0 | 0 | 1 | 1 | A#B | |

| 1 | 0 | 1 | 0 | A—B | 0 | 0 | 1 | 0 | A&B | |

| 1 | 0 | 0 | 1 | RL | 0 | 0 | 0 | 1 | A+1 | |

| 1 | 0 | 1 | 0 | RR | 0 | 0 | 0 | 0 | A | |

四、设置初始状态

K23~K0置“0”,灭M23~M0控位显示灯。

示例1 算术运算

1. 字算术运算

(1) 字写操作(置数操作)

通过“I/O单元”二进制开关向寄存器AX和BX置数,操作步骤如下:

(2) 字读操作(运算寄存器AX和BX内容送总线)

(3) 字算术运算(不带进位加)

令M S2 S1 S0(K15 K13~K11=1011),FUN及总线单元显示AX+BX的结果。

令M S2 S1 S0(K15 K13~K11=1010),FUN及总线单元显示AX-BX的结果。

2. 字节算术运算

(1) 偶字节写(置数操作)

拨动“I/O输入输出单元”开关向寄存器AL和BL置数,操作步骤如下:

(2) 偶字节读操作(运算寄存器AL和BL内容送总线)

(3) 偶字节减法运算(不带进位加)

令M S2 S1 S0(K15 K13~K11=1011),FUN及总线单元显示AL+BL的结果。

令M S2 S1 S0(K15 K13~K11=1010),FUN及总线单元显示AL-BL的结果。

示例2 逻辑运算

1. 字逻辑运算

(1) 字写操作(置数操作)

拨动“I/O输入输出单元”开关向寄存器AX和BX置数,操作步骤如下:

(2) 字读操作(运算寄存器AX和BX内容送总线)

(3) 字逻辑运算

令M S2 S1 S0(K15 K13~K11=0010),为逻辑与,FUN及总线显示AX逻辑与BX的结果。

令M S2 S1 S0(K15 K13~K11=0011),为逻辑或,FUN及总线显示AX逻辑或BX的结果。

2. 字节逻辑运算

(1) 偶字节写操作(置数操作)

拨动“I/O输入输出单元”开关向寄存器AL和BL置数,具体操作步骤如下:

(2) 偶字节读操作(运算寄存器AL和BL内容送数据总线)

① 若运算控制位设为(M S2 S1 S0=0000)则F=AL,即AL内容送到数据总线。

② 若运算控制位设为(M S2 S1 S0=0111)则F=BL,即BL内容送到数据总线。

(3) 偶字节逻辑运算

令M S2 S1 S0(K15 K13~K11=0010),为逻辑与,FUN及总线显示AL逻辑与BL的结果。

令M S2 S1 S0(K15 K13~K11=0011),为逻辑或,FUN及总线显示AL逻辑或BL的结果。

(4) 奇字写操作(置数操作)

拨动“I/O输入输出单元”开关向寄存器AH和BH置数,操作步骤如下:

(5) 奇字节读操作(运算寄存器AH和BH内容送总线)

关闭AH、BH写使能,令K17=K18=1,按下流程分别读AH、BH。

① 若运算控制位设为(M S2 S1 S0=0000)则F=AH,即AH内容送到数据总线。

② 若运算控制位设为(M S2 S1 S0=0111)则F=BH,即BH内容送到数据总线。

(6) 奇字节逻辑运算

令M S2 S1 S0(K15 K13~K11=0010),为逻辑与,FUN及总线显示AH逻辑与BH的结果。

令M S2 S1 S0(K15 K13~K11=0011),为逻辑或,FUN及总线显示AH逻辑或BH的结果。

实验思考

验证表2.4.2 ALU运算器编码表所列的运算功能。

在给定AX=6655h、BX=AA77h的情况下,改变运算器的功能设置,观察运算器的输出,填入下页表格中,并和理论分析进行比较、验证。

| 表2.4.2 ALU运算器真值表 | ||||||||

| 运算控制 | 运算表达式 | K15 | K13 | K12 | K11 | AX | BX | 运算结果 |

| M | S2 | S1 | S0 | |||||

| 带进位算术加 | A+B+C | 1 | 1 | 1 | 1 | 6655 | AA77 | FUN=( 10CC ) |

| 带借位算术减 | A-B-C | 1 | 1 | 1 | 0 | 6655 | AA77 | FUN=( BBDE ) |

| 带进位左移 | RLC A | 1 | 1 | 0 | 1 | 6655 | AA77 | FUN=( CCAA ) |

| 带进位右移 | RRC A | 1 | 1 | 0 | 0 | FUN=( ) | ||

| 算术加 | A+B | 1 | 0 | 1 | 1 | FUN=( ) | ||

| 算术减 | A-B | 1 | 0 | 1 | 0 | FUN=( ) | ||

| 左移 | RL A | 1 | 0 | 0 | 1 | FUN=( ) | ||

| 右移 | RR A | 1 | 0 | 0 | 0 | FUN=( ) | ||

| 取BX值 | B | 0 | 1 | 1 | 1 | 6655 | AA77 | FUN=( AA77 ) |

| AX取反 | NOT A | 0 | 1 | 1 | 0 | 6655 | AA77 | FUN=( 99AA ) |

| AX减1 | A-1 | 0 | 1 | 0 | 1 | 6655 | AA77 | FUN=( 6654 ) |

| 清零 | 0 | 0 | 1 | 0 | 0 | FUN=( ) | ||

| 逻辑或 | A OR B | 0 | 0 | 1 | 1 | FUN=( ) | ||

| 逻辑与 | A AND B | 0 | 0 | 1 | 0 | FUN=( ) | ||

| AX加1 | A+1 | 0 | 0 | 0 | 1 | FUN=( ) | ||

| 取AX值 | A | 0 | 0 | 0 | 0 | FUN=( ) | ||

示例3 移位运算

本示例以累加器AX为移位的源与目的寄存器,也就是说移位是通过累加器AX实现的,这种规范的设计理念使我们的运算器能够与通用计算机指令系统相吻合。

1. 移位执行过程

所谓循环移位,就是指移位时数据的首尾相连进行移位,即最高(最低)位的移出位又移入数据的最低(最高)位。根据循环移位时进位位是否一起参加循环,可将循环移位分为不带进位循环和带进位循环两类。其中不带进位循环是指进位“CY”的内容不与数据部分一起循环移位,也称小循环。带进位循环是指进位 “CY”中的内容与数据部分一起循环移位,也称大循环。

◆不带进位循环左移:各位按位左移,最高位移入最低位。

◆不带进位循环右移:各位按位右移,最低位移入最高位。

◆带进位循环左移:各位按位左移,最高位移入C中,C中内容移入最低位。

◆带进位循环右:各位按位右移,最低位移入C中,C中内容移入最高位。

循环移位一般用于实现循环式控制、高低字节的互换,还可以用于实现多倍字长数据的算术移位或逻辑移位。

2. 移位运算实例

① K23~K0全置“0”,灭M23~M0灯。

② 累加器AX置数与移位流程

③ 字移位:完成上流程,按下表改变S2(K13)、S0(K11)的状态,再按【单拍】钮,观察AX的移位变化。

④ 字节移位:完成字移位后,改变字长宽度,令W(K6)=0,然后根据下表设置S2(K13)、S0(K11)的电位,再按【单拍】钮,AX进入字节移位状态,观察AL的移位变化。

| 表2.4. 3 移位编码表 | ||||

| K15 | K13 | K12 | K11 | 功能 |

| M | S2 | S1 | S0 | |

| 1 | 0 | 0 | 0 | RR |

| 1 | 0 | 0 | 1 | RL |

| 1 | 1 | 0 | 0 | RRC |

| 1 | 1 | 0 | 1 | RLC |

示例4 进位控制与零标志

1. 标志控制原理

图2-4-2 标志位锁存原理图

(1) 进位标志CY

运算标志CY是带复位可预置的进位标志,在运算时由M信号控制,当M=1时,按【单拍】按钮,在T4上升沿把当前运算溢出位(进位或借位)打入CY的锁存输出端Q2;当M=0时,由CN位控制CY的“位操作”。当CN=1,按【单拍】按钮,在T4上升沿执行CY的置位、清零、取反操作;遇M=0、CN=0时,CY保持原始状态。CY的复位端由管理CPU直接控制。

(2) 零标志Z

零标志Z是带复位端的运算结果判零标志,取源于运算器输出FUN。当运算输出FUN为0时,zd为“1”,反之为“0”;零标志由M信号控制,当M=1时,按【单拍】按钮,在T4上升沿把当前zd打入Z(零标志)的锁存输出端Q1;当M=0时,零标志Z保持原始状态。

(3) 标志位的初始化

标志位的清零端由系统掌控与控位无关,在手动实验中需要清标志时,通过按动【返回】键来实现标志位的初始化。

系统提供CY与Z的状态灯,其显示特征为:进位标志CY=“1”时,灯“亮”反之灯“灭”;零标志Z=“1”时,灯“亮”反之灯“灭”。

2. 进位控制实验

① 进位控制流程

② 进位控制实验

置位操作:当M、CN、XP、W=0100时,按【单拍】按钮,CY=1(灯亮);

清零操作:当M、CN、XP、W=0110时,按【单拍】按钮,CY=0(灯灭);

取反操作:当M、CN、W=100时,每按一次【单拍】按钮,CY=/CY(取反)。

3. 进位运算实验

① 按【返回】键,实现进位及零标志清零。通过“I/O单元”向AX、BX置数。

② 进位标志锁存

K23~K0置全“0”,关闭M23~M0控位灯。令X0、W=11,运算控位M、S2、S1、S0 =1111,按【单拍】按钮,FUN显示带进位加结果,进位标志灯CY亮,表示有进位。

完成上流程,按【单拍】钮,ALU执行A+B+CY的操作,FUN=0002、CY=1(灯亮)。

令S0为0,按【单拍】钮,ALU执行A-B-CY的操作,FUN=FFFB、CY=0(灯灭)。

1. 零标志实验

① K23~K0置全“0”,通过“I/O单元”向AX、BX均置数0001h,操作步骤如下:

② 零标志锁存

K23~K0置全“0”,灭M23~M0控位灯。令X0=1,运算控位M、S1=11,按【单拍】按钮,FUN显示算术减结果,其零标志Z的灯亮,表示运算结果为零。

2. 标志位的字节运算

令W(K6)=“0”,参照进位与零标志运算流程,ALU按字节方式建立和锁存CY及Z标志。

实验四:十六位数据总线实验

一、实验目旳

1. 熟悉和了解总线的数据通路、双向互递原理及寻址方式与运用规则。

2. 掌握十六位数据总线中“字”与“字节”操作方法及源与目的奇偶效应。

二、实验要求

通过总线的数据传递实验,建立“奇偶”概念,领会字寻址中对字节操作的动态定义。

三、实验原理

系统数据总线作为计算机传递信息的通道是连接各个功能部件的纽带,在计算机中起着至关重要的作用。模型机的工作过程就是计算机各个功能部件之间的信息,通过数据总线不断有序流动的过程。

图2-3-8 系统体系结构图

1. 字与字节体系

本系统总线宽度为十六位,设有字长控位“W”,当W=1,由源寻址的奇偶性决定当前总线宽度,遇源址为偶时其字长宽度为十六位;当源址为奇或W=0时,字长宽度为八位,形成图2-3-9所示的奇(八位)与偶(八位)互通的字节总线。

图2-3-9 奇偶互通字节总线体系结构图

2. 源奇偶的运用

图2-3-9所示,我们按原理计算机的设计规范,以字节为基准把十六位数据总线划分奇与偶俩路八位总线,其中“D15~D8”称为“奇总线”,“D7~D0”称为“偶总线”;在字节传递中由于总线的互通,形成“奇送偶”或“偶送奇”的八位字节总线,其使能端定义为低电平选通,逻辑表达式为:

G(偶字节)= !W(字长)# XP(源奇偶)

G(奇字节)= !XP(源奇偶)

从上俩式可知,图2-3-9所示的奇偶总线由字长“W”和源奇偶“XP”动态呈现以下三状态:

⑴ 在W=1时遇XP=1,由于G(偶字节)与G(奇字节)处隔离态“1”,形成“D15~D0”十六位字总线源。

⑵ 在W=0时遇XP=1,由于G(偶字节)为“0”,G(奇字节)“1”,形成“偶送奇‘的八位字节总线源。

⑶ 在XP=0时,由于G(奇字节)为“0”,G(偶字节)为“1”,无条件形成“奇送偶”的八位字节总线源。

3. 目的奇偶的运用

在目的寻址中亦由字长控位“W”与目的地址的奇偶性动态定义当前目的字长。在W=0又遇目的址为偶时,其目的传递为字操作,否则均为字节传递,其逻辑表达式为:

!O(偶字节)= !OP(目的奇偶)

!O(奇字节)= !W(字长)# OP(目的奇偶)

上述俩式表明,由字长“W”和目的址奇偶“OP”动态产生以下三种目的寻址操作

⑴ 在W=1时遇OP=1,由于O(偶字节)与O(奇字节)均为“0”,执行以当前目的偶址为目标的字传递。

⑵ 在W=0时遇OP=1,由于O(偶字节)=“0”、O(奇字节)=“1”,执行以当前目的偶址为目标的字节传递。

⑶ 在OP=0时,由于O(奇字节)=“0”、O(偶字节)=“1”,无条件执行以当前目的奇址为目标的字节传递。

4. 数据传递规则

系统在十六位原理计算机的字操作中动态地融入了字节操作的过程,其源奇偶映射总线宽度,而目的奇偶则制约传递长度。系统在十六位原理计算机的字节操作中运用总线互联机制,以源址的奇偶性形成“奇递偶”或“偶递奇”两者互通的八位字节总线。

| 表2.3.7 十六位总线传递规则 | |||

| 总线规则 | 功能说明 | ||

| W | XP | OP | |

| 1 | 1 | 1 | 字传递(十六位传递) |

| 0 | 1 | 1 | 偶送偶(低位送低位) |

| 0 | 1 | 0 | 偶送奇(低位送高位) |

| X | 0 | 1 | 奇送偶(高位送低位) |

| X | 0 | 0 | 奇送奇(高位送高位) |

说明:上表中“XP”与“OP”仅为原理计算机特定的专用寄存器奇偶标志,适用于AX、BX、SP及I/O的寻址场合;在存储器寻址中应以地址线“A0”为奇偶;在通用寄存器寻址中应从指令格式中所定义的“源与目的”字段动态索取奇偶标志。

四、数据传递实验

1. 实验连线

| 连线 | 信号孔 | 接入孔 | 作用 | 有效电平 |

| 1 | DRCK | CLOCK | 单元手动实验状态的时钟来源 | 下降沿打入 |

| 2 | W | K6(M6) | 总线字长:1=16位字操作,0=8位字节操作 | |

| 3 | XP | K7(M7) | 源部件奇偶标志:1=偶寻址,0=奇寻址 | |

| 4 | X2 | K10(M10) | 源部件定义译码端X2 |

三八译码 八中选一 |

| 5 | X1 | K9(M9) | 源部件定义译码端X1 | |

| 6 | X0 | K8(M8) | 源部件定义译码端X0 | |

| 7 | OP | K16(M16) | 目标部件奇偶标志:1=偶寻址,0=奇寻址 | |

| 8 | AXW | K17(M17) | AX运算寄存器写使能,本例定义到M17位 | 高电平有效 |

2. 十六位数据传送(字传递)

设置数据来源为I/O单元(X2 X1 X0=011),总线规则设为字传递(W XP OP=111),打开AX写使能(AXW(M17)=1),拨动“I/O输入输出单元”十六位数据开关,按【单拍】按钮,将I/O单元内容通过数据总线传递到AX寄存器,操作步骤如下:

3. 低位到低位(偶送偶)

设置数据来源为I/O单元(X2 X1 X0=011),总线规则设为偶送偶(W XP OP=011),打开AX写使能(AXW(M17)=1),拨动“I/O输入输出单元”十六位数据开关,按【单拍】按钮,将I/O偶单元内容通过数据总线传递到AL寄存器,操作步骤如下:

4. 低位到高位(偶送奇)

设置数据来源为I/O单元(X2 X1 X0=011),总线规则设为偶送奇(W XP OP=010),打开AX写使能(AXW(M17)=1),拨动“I/O输入输出单元”十六位数据开关,按【单拍】按钮,将I/O偶单元内容通过数据总线传递到AH寄存器,操作步骤如下:

5. 高位到低位(奇送偶)

设置数据来源为I/O单元(X2 X1 X0=011),总线规则设为奇送偶(W XP OP=X01),打开AX写使能(AXW(M17)=1),拨动“I/O输入输出单元”十六位数据开关,按【单拍】按钮,将I/O奇单元内容通过数据总线传递到AL寄存器,操作步骤如下:

6. 高位到高位(奇送奇)

设置数据来源为I/O单元(X2 X1 X0=011),总线规则设为奇送奇(W XP OP=X00),打开AX写使能(AXW(M17)=1),拨动“I/O输入输出单元”十六位数据开关,按【单拍】按钮,将I/O奇单元内容通过数据总线传递到AH寄存器,操作步骤如下:

实验五:地址总线组成实验

一、实验目旳

1. 熟悉和了解地址总线的组成结构、地址来源及集合原理。

2. 掌握程序段与数据段的寻址规则及地址部件的运用技巧。

二、实验要求

通过地址形成部件实验,建立“段”概念,学会“段”运用。

三、实验原理

地址总线的作用是传递地址信息,输出当前数据总线上发送信息的源地址或接收信息的目的地址。如下图所示本系统设有内存与外设两条地址总线,通过PC计数器提供内存(程序存储器)地址,并由地址寄存器AR传递内存(数据存储器)地址与外设地址。另外堆栈寄存器SP亦可视为地址寄存器,它的堆顶指向数据与程序指针存取地址。

图2-3-6 地址总线组成通路

1. 11位程序地址

如图2-3-6所示,本系统从提高信息存取效率的角度设计主内存地址通路,按现代计算机体系结构中最为典型的分段存取理念合成主存及外设地址总线addr,在指令操作“时段”(取操作码与取操作数),以当前程序指针PC为址,遇主存数据传递“时段”以当前数据指针AR为址。addr地址的合成通路见图2-3-6。其寻址范围为0~7FFh。

2. 16位数据地址

如图2-3-6所示,本系统数据指针由地址锁存器AR直接提供,当LDAR=1时,在DRCK下降沿把数据总线打入AR。其寻址范围为0~FFFFh,可达64KB。

四、地址部件电路

图2-3-7 地址部件控制电路

五、实验内容

1. 程序计数器实验

| 表2.3.7 PC程序计数器目标编码 | |||

| 目标部件定义 | 按钮 | 功能说明 | |

| E/M | IP | DRCK | DRCK下降沿打入 |

| 0 | 0 | X | PC保持 |

| 0 | 1 | ↓ | PC加1 |

| 1 | 1 | ↓ | PC装载 |

| 说明:“↓”表示下降沿有效 | |||

图2-3-7所示的PC框由3片161构成按字方式寻址的11位PC计数器,计数器的输入端与总线相连构成置数通路,计数器的输出端途经三态门缓冲分离为两条通路,其一与总线相连构成可读通路,其二与地址寄存器(数据)集合组成主存EM地址总线。它的清零端由中央外理器单元直控,上电时PC计数器自动淸零,实验中按复位钮亦可实现计数器的手动淸零。

手控状态,本实验由表2.6.1定义的目的编码控制PC计数器的预置与加1操作,并以准双向I/O部件的S10~S0为计数器预置源。当IP=1时按单拍按钮,遇E/M=1在脉冲下降沿把S10~S0的内容装入PC计数器;遇E/M=0在脉冲下降沿PC计数器加1。

PC计数器的读出操作由表2.3.7所列的源编码表定义。

1)实验连线

| 连线 | 信号孔 | 接入孔 | 作用 | 有效电平 |

| 1 | DRCK | CLOCK | 单元手动实验状态的时钟来源 | 下降沿打入 |

| 2 | W | K6(M6) | 总线字长:1=16位字操作,0=8位字节操作 | |

| 3 | XP | K7(M7) | 源奇偶位:1=偶寻址,0=奇寻址 | |

| 4 | OP | K16(M16) | 目的奇偶位:1=偶寻址,0=奇寻址 | |

| 5 | X2 | K10(M10) | 源部件定义译码端X2 |

三八译码 八中选一 |

| 6 | X1 | K9(M9) | 源部件定义译码端X1 | |

| 7 | X0 | K8(M8) | 源部件定义译码端X0 | |

| 8 | LDPC | K22(M22) | PC程序计数器刷新位 | 高电平有效 |

| 9 | E/M | K23(M23) | 当IP有效时,E/M:1=PC装载,0=PC加1 | |

| 10 | SPW | K20(M20) | SP堆栈指针写使能 | 高电平有效 |

| 11 | LDAR | K19(M19) | AR地址寄存器写使能 | 高电平有效 |

2)程序计数器PC的写入、读出与加1

(1) PC程序计数器的写入

通过“I/O单元”开关向程序计数器PC置数,操作步骤如下:

(2) PC程序计数器的读出

在PC置数操作完成后,按上流程中后两步的要求,关闭PC写使能(K23、K22=00),打开PC输出三态门(K10~K6=11111),数据总线单元应显示的PC指针为0100h。

(3) PC程序计数器加1

在保持PC置数与读出流程的状态下,令K22=1,按【单拍】按钮,在DRCK节拍的下降沿PC计数器加1并送数据总线,PC程序计数器和数据总线单元的显示器应显示0101h。继续按【单拍】按钮,观察PC与数据总线的内容。

2、地址寄存器实验

图2-3-7所示的AR框由2片74LS574锁存器构成按字方式寻址的16位数据指针,锁存器的输入端与总线相连构成置数通路,锁存器的输出端途经三态门缓冲分离与PC计数器集合组成主存地址总线。它的清零端由中央外理器单元直控,上电时锁存器自动淸零,手动实验中按【返回】键亦可实现锁存器的手动淸零。按通用计算机设计规范的要求,把数据指针AR定义为字写入寄存器,运用中局限于字写,字节写会引发数据指针的错误侵入,因此在数据指针AR的操作过程中并非不支持而是不允字节写。

地址寄存器AR打入

在手控/搭接态,数据指针AR由W、LDAR及DRCK(CP脉冲)三信号组合控制地址的置数操作。本实验以总线上准双向I/O部件的S15~S0为置数源。当W=1、LDAR=1时按【单拍】钮,在脉冲下降沿把S15~S0的内容装入地址锁存器AR。操作步骤如下:

3、堆栈寄存器实验

图2-3-7所示的SP框由2片74LS574锁存器构成16位堆栈指针,锁存器的输入端与总线相连构成存数通路,锁存器的输出端途经三态门隔离与总线相连构成取数通路。它按先进后出的原则存放需要保留的数据信息与地址信息,在调用中断等突发事件处理中SP指针以间址方式把当前程序指针存入SP-2单元,遇返回指令SP又把栈项所指单元的内容装入程序计数器,然后SP+2退至原始位置。

在手控/搭接态,堆栈指针SP由W、SPW及DRCK(CP脉冲)三信号组合控制栈指针的置数操作。本实验以总线上准双向I/O部件的S15~S0为置数源。当W=1、SPW=1时按单柏钮,在脉冲下降沿把S15~S0的内容装入SP。

堆栈指针SP的读出操作由P8页表2.2所列的源编码表定义。

1)堆栈指针SP打入

拨动“I/O输入输出单元”开关向堆栈指针SP置数,具体操作步骤如下:

2)堆栈指针SP读出

关闭SP写使能,令SPW=1 按下流程完成SP送总线。

实验六:存储器读写实验

一、实验目的

熟悉和了解存储器组织与总线组成的数据通路。

二、实验要求

按照实验步骤完成实验项目,掌握存储部件在原理计算机中的运用。

三、实验原理

存储器是计算机的存储部件,用于存放程序和数据。存储器是计算机信息存储的核心,是计算机必不可少的部件之一,计算机就是按存放在存储器中的程序自动有序不间断地进行工作。

本系统从提高存储器存储信息效率的角度设计数据通路,按现代计算机中最为典型的分段存储理念把存储器组织划分为程序段、数据段等,由此派生了数据总线(DBUS)、指令总线(IBUS)、微总线(mBUS)等与现代计算机设计规范相吻合的实验环境。

实验所用的存储器电路原理如图2-3-10所示,该存储器组织由二片6116构成具有奇偶概念的十六位信息存储体系,该存储体系AddBus由PC指针和AR指针分时提供,E/M控位为“0”时选通PC,反之选通AR。该存储体系可随机定义总线宽度,动态变更总线结构,把我们的教学实验提高到能与现代计算机设计规范相匹配与接轨的层面。

图2-3-10 存储器数据通路

四、存储器分类与寻址

1. 存储器组织分类表

本系统主存储器由两个部分组成,详见下表:

| 分类 | 存储容量 | 寻址范围 |

| 程序段 | 2K | 0~7FFh |

| 数据段 | 2K | 0~7FFh |

2. 程数存储器源与目的寻址

| 程序段与数据段源寻址 | 程序段与数据段目的寻址 | |||||||||||

| 源使能 | 源编址 | 注释 | 目的编址 | 注释 | ||||||||

| X2 | X1 | X0 | E/M | W | A0 | MWR | E/M | W | A0 | |||

| 1 | 0 | 0 | 0 | 1 | 0 | 程序段字读 | 1 | 0 | 1 | 0 | 程序段字写 | |

| 0 | 0 | 程序段偶读 | 0 | 0 | 程序段偶写 | |||||||

| X | 1 | 程序段奇读 | X | 1 | 程序段奇写 | |||||||

| 1 | 1 | 0 | 数据段字读 | 1 | 1 | 0 | 数据段字写 | |||||

| 0 | 0 | 数据段偶读 | 0 | 0 | 数据段偶写 | |||||||

| X | 1 | 数据段奇读 | X | 1 | 数据段奇写 | |||||||

| 注:在【单拍】按钮下降沿写入 | ||||||||||||

五、实验内容

1. 实验连线

| 连线 | 信号孔 | 接入孔 | 作用 | 有效电平 |

| 1 | DRCK | CLOCK | 单元手动实验状态的时钟来源 | 下降沿打入 |

| 2 | W | K6(M6) | 总线字长:1=16位字操作,0=8位字节操作 | |

| 3 | XP | K7(M7) | 源部件奇偶标志:1=偶寻址,0=奇寻址 | |

| 4 | X2 | K10(M10) | 源部件定义译码端X2 |

三八译码 八中选一 |

| 5 | X1 | K9(M9) | 源部件定义译码端X1 | |

| 6 | X0 | K8(M8) | 源部件定义译码端X0 | |

| 7 | E/M | K23(M23) | 存储器地址段定义:1=AR指针,0=PC指针 | |

| 8 | MWR | K21(M21) | 存储器写使能:1=存储器写 | |

| 9 | LDAR | K17(M17) | AR地址寄存器写使能 | 高电平有效 |

| 10 | LDPC | K22(M22) | PC装载与PC+1 | 高电平有效 |

2. 存储器数据段读写操作

(1) 数据段写操作(字)

在进行数据存储器字操作时,地址线A0必须为0(偶地址)。向数据段的0000~0005h存储单元写入11 22 33 44 55 66一串数据,以0000h地址单元写入数据1122h为例表述操作流程。

按照上述操作流程完成0002~0005h单元分别写入33 44 55 66的操作。

(2) 数据段读操作(字)

依次读出数据段0~0005h单元的内容,这里以0000h地址单元读出为例阐述操作流程。

执行上述流程总线单元应显示1122h,若正确可按上述流程读出0002~0005h单元的内容。

3. 存储器程序段读写操作

(1) 程序段字节写操作

① 计算机规范的取指操作均以字节为单位。所以本实验以字节操作方式展开。程序段写入必须从定义地址入手,然后再进入程序存储器的写入。

② PC指针是带预置加法计数器,因此在输入起始地址后一旦后续地址为PC+1的话就不需重装PC,用PC+1指令完成下续地址的读写操作。

③ PC地址装载写入与PC+1写入流程

按照上述PC装载写入与PC+1写入的流程分别对0000~0003h写入12 34 56 78。

(2) 程序段字节读操作

PC地址装载读出及PC+1读出流程

按照上述PC装载读出与PC+1读出的流程分别读出0000~0003h单元内容,应为12345678h。